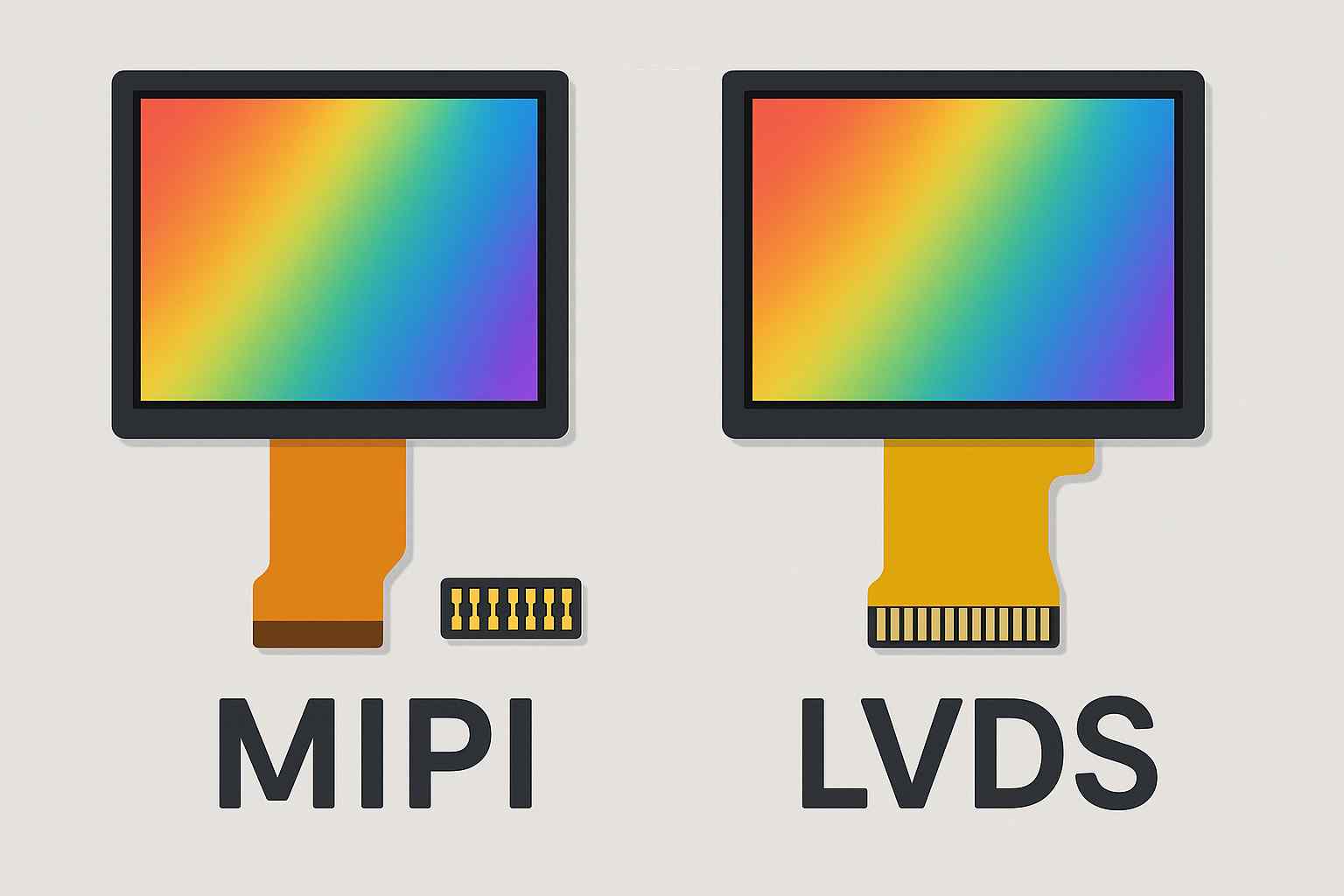

1920×1080TFT-LCD10.1寸工业液晶屏,eDP,LVDS怎么选

2026-02-26

LCD液晶屏,LCD10.1寸1920×1080TFT-LCD工业液晶屏选型不止看接口名,更要看“链路能力”和“交付风险”,做10.1寸1920×1080(FHD)TFTLCD液晶屏选型时,很多人会把问题简化成一句:“主板有eDP就用eDP,旧板子只有LVDS就用LVDS。”这句话并不算错,但它解释不了你真正会遇到的工程现实:

同样是10.1寸FHD,有的项目eDP一次点亮、量产稳定;也有项目eDP偶发黑屏/花屏、EMI一来就掉链路。LVDS也一样:有人觉得它“简单稳定”,有人却在JEIDA/VESA映射、单/双通道、线束对绞与地回流上反复返工。

更接近真相的说法是:

10.1寸FHD的难点不在“分辨率”,而在“数据率+线束/EMI边界+接口协议复杂度”。eDP与LVDS的差异,本质是两条完全不同的交付路线:

1·eDP:协议更完整、链路可伸缩,但对链路训练与信号完整性更敏感;

2·LVDS/OpenLDI:映射固定、行为可预测,但线对更多、映射/位宽/单双通道更容易“同名不同义”。

下面用一个“能落地”的框架,把eDP/LVDS的选择讲透:怎么算账、怎么问供应商、怎么把风险写进规格书,避免“同尺寸同分辨率却不兼容”。

1、10.1寸FHD到底需要多大链路能力?

FHD1920×1080@60Hz是最常见的基础目标。参考VESADMTRev.13里收录的1080p(CEA-861Code16)时序给出像素时钟PixelClock=148.500MHz。

这行数字的价值在于:它让你能快速判断“LVDS够不够、是否要双通道”“eDP用几条lane才稳”。不管你最后用什么接口,链路要承载的像素节拍大概率就在这个量级(具体还会受porch/blanking、刷新率、色深影响)。

2、LVDS:

10.1寸FHD用LVDS,真正要确认的是“几线+单/双通道+映射”

2.1“几线LVDS”

“几线LVDS”不是口头概念,它对应OpenLDI的数据线数量,OpenLDI(LVDS显示接口的一套经典定义)写得非常直接:

18-bit单像素:用A0~A2

24-bit单像素:用A0~A3

18-bit双像素:用A0~A2以及A4~A6

24-bit双像素:用A0~A7并且:每根串行数据线的比特率是像素时钟的7倍;双像素模式下CLK2也会携带像素时钟。

这段话翻译成工程语言就是:

你看到规格写“4线LVDS”,很多时候等价于24-bit单像素(A0~A3);

你看到“8线/双通道LVDS”,很多时候等价于24-bit双像素(A0~A7);

FHD这种数据率,如果用LVDS单通道24-bit,数据线速率会被推得很高:按OpenLDI的“7×像素时钟”,148.5MHz对应每条串行数据线约1.0395Gbps(不含编码开销),这对线束、对间偏斜、接地回流与EMI都会更敏感(这也是很多FHDLVDS项目容易变成“双通道/双像素”的原因)。

2.218-bitvs24-bit:

18-bitvs24-bit:不仅是颜色多少,还是“线数/映射规则”差异,在TI的LVDS/FPD-Link映射资料明确写到:18-bit只需要3条LVDS串行数据线,而24-bit使用4条LVDS数据线;24-bit多出来的LSB映射到第4条LVDS数据线。

这就是在替代屏时常见“能亮但偏色、灰阶断层”的根源之一:位宽不一致+映射不一致,画面不是“差一点”,而是“解释规则错了”。

2.3JEIDA/VESA映射:

JEIDA/VESA映射:不看bitmapping图就等于没核对,行业里最常见的坑:同样写着“LVDS40pin”,但JEIDA/VESA映射不同。你如果只凭“接口类型一致”去替换,非常容易出现偏色/花屏。工程上最稳的做法是:把面板datasheet的bitmapping图要到手,和主板输出的映射模式逐位对照(这一步比“换线试试”省得多)。

3、eDP:

10.1寸FHD选eDP,你买的是“协议能力”,不是“几根线”,eDP本质上是DisplayPort体系在嵌入式显示上的应用。VESA的eDPDevCon材料讲得很实在:

eDP复用DisplayPortGPU接口,不需要像LVDS那样占用专用视频口

主链路MainLink的lane数可在1~4lanes之间按数据率伸缩

AUX与HPD作为旁带通道,用于显示配置与控制这三点决定了eDP的工程特性:

更“体系化”:链路能力可调,生态更现代(尤其在x86/笔电/工控板/部分ARMSoC上);

更“软件化”:AUX/HPD、训练、配置都让它不像LVDS那样“插上就定死”,而更像一个会协商的链路。

3.1eDP为什么有时会“偶发黑屏/重连”?

参考VESA的DisplayPort技术概览里提到:AUX用于维持链路,Sink可以通知Source主链路数据损坏,Source可以重新发起链路训练来恢复链路。

而TI的应用笔记也明确指出:DP的AUX通道用于Source与Sink的双向通信,用于DPlinktraining来优化通道配置。

这意味着:

eDP在“链路质量边界”附近(线束稍长、连接器批次差异、供电噪声、强EMI)可能出现“看似随机”的不稳定;

但反过来,eDP也具备更强的链路管理手段(训练、均衡、恢复),在成熟平台上反而更容易做成“规模化稳定”。

4、10.1寸FHD:

eDPvsLVDS的真实差别,下面这张对照表,可以直接拿去做选型评审(参考):

| 维度 | eDP | LVDS/OpenLDI |

| 体系属性 | 协议化(AUX/HPD/训练/配置) | 映射化(位宽+映射+通道组织固定) |

| 带宽扩展 | 通过lane数/速率档伸缩(1~4lanes) | 通过单/双通道(单像素/双像素)与线数扩展 |

| 线束与连接器 | 对高速SI要求高,但线对数量相对少(常见30pin) | 线对数量多、对间偏斜与地回流管理更关键;FHD常见要双通道/更多对数 |

| 兼容性风险点 | 链路训练边界、供电噪声/EMI导致掉链路 | JEIDA/VESA映射、18/24-bit位宽、单/双通道、线序极性不一致 |

| 调试方式 | 更依赖协议层信息(训练状态、AUX事务) | 更依赖硬件对照(bitmapping、差分对/时钟/极性、时序) |

| 适配生态 | 新平台/笔电/部分工控板更友好 | 旧平台/大量传统工控板更友好 |

一个更“反直觉”的结论:

如果追求“工程确定性”,LVDS看似简单,但在FHD这个数据率门槛上,它往往把复杂度转移到了“线束/映射/单双通道一致性”上;

eDP看似复杂,但在成熟主板平台与短距离线束场景里,反而可能更省集成时间。

5、10.1寸1920×1080的“3步选型法”

第一步:主板能稳定输出什么

别先问“你们有啥屏”,先问“我的主板能稳输出啥”:

有无原生eDP?支持几lanes?是否能读EDID、是否支持面板上电/背光时序?

LVDS:输出是18-bit还是24-bit?JEIDA还是VESA?单通道还是双通道?

输出时序能否调整?(至少能把1080p的像素时钟量级对齐:VESADMT里1080p@60的PixelClock是148.5MHz。)

如果主板端输出能力不清晰,后面所有“屏选型”都是盲选。

第二步:屏“接受规则”是什么

对eDP屏:

eDP版本/训练策略(是否需要完整训练、是否支持快训/无训)

lane数需求(1/2/4)与面板上电时序要求

是否需要AUX控背光、还是外部PWM/EN

对LVDS屏:

单/双通道(单像素/双像素)

位宽(18/24)

映射口径(JEIDA/VESA)

对应OpenLDI的“用几条数据线”:单像素24-bit用A0~A3,双像素24-bit用A0~A7;每条数据线速率为7×像素时钟

第三步:“成本/交期/二供”

在工业液晶屏的交付里,真正的大钱往往不在单价,而在返工与售后:

eDP:要评估线束长度、走线路径与EMI边界;因为链路维护/训练机制会把“边界问题”表现为偶发。

LVDS:要评估线束对数、对间偏斜、接地回流与映射一致性;因为FHD常把LVDS推到较高数据线速率(7×像素时钟),任何“线束不规范”都会被放大。

6、10.1寸FHD也存在LVDS形态

很多渠道会误以为“10.1FHD必然eDP”。实际上市场上确实存在10.1寸1920×1080的LVDS模组形态,例如某些40pinLVDS产品页会明确写10.1"、1920×1080、LVDS40PIN等参数(用于工业嵌入式)。

这类屏能不能用,关键不在“有没有LVDS”,而在有没有把位宽/映射/单双通道/时序写清楚并验证。

7、询价单了解项

你可以把下面内容直接复制到询价单/规格书里:

1.尺寸与分辨率:10.1"/1920×1080/目标刷新率(如60Hz)

2.目标时序:至少确认像素时钟量级(VESADMT中1080p@60PixelClock=148.5MHz)

3.接口:eDP或LVDS

4.若eDP:lane数范围(1–4)、AUX/HPD控制方式、是否支持快训/无训

5.若LVDS:18/24-bit、JEIDA/VESA、单/双通道(单/双像素)、bitmapping图必须提供

6.线束与连接器:连接器型号、线束长度上限、出线方向与弯折半径

7.背光:是否内置LEDdriver、PWM/EN口径与上电时序

8.可靠性:工作温度、震动冲击、ESD目标(触摸屏另列)

9.供货:生命周期、PCN变更机制、可替代料建议

8、常见问题

Q1:10.1寸1920×1080用LVDS一定要双通道吗?

不一定,但要看你面板/主板对OpenLDI/LVDS的实现方式。OpenLDI允许24-bit单像素用A0~A3,也允许24-bit双像素用A0~A7,且每条数据线速率是像素时钟的7倍;FHD在148.5MHz像素时钟量级下,单通道会把线束与SI压力推高,所以工程上常见用“双像素/双通道”来换取裕量。

Q2:eDP为什么有时会出现偶发黑屏/重连?

因为eDP/DP通过AUX进行链路维护与训练;当链路出现数据损坏时,源端可能重新发起链路训练以恢复链路。线束、连接器、供电噪声、EMI都可能把系统推到边界。

Q3:LVDS最容易写错的规格是什么?

位宽(18/24-bit)与映射口径(JEIDA/VESA)最常见。相关映射资料明确指出18-bit只需3条LVDS数据线,而24-bit用4条,多出的LSB映射到第4条数据线。不写清楚就容易“能亮但偏色/灰阶断层”。

Q4:同样是1080p,为什么“同分辨率不兼容”?

分辨率相同只代表像素数相同,不代表:时序(像素时钟、porch、极性)、映射(bitmapping)、通道组织(单/双通道)相同。10.1寸FHD的兼容性,往往就卡在这些“协议细节”上。

Q5:到底什么时候优先选eDP,什么时候优先选LVDS?

主板原生eDP、线束短、希望简化线对数量与供货生态:优先eDP(lane数可伸缩,AUX/HPD便于配置控制)。

是LVDS存量平台、固件/驱动不可改、追求行为可预测:优先LVDS,但必须把位宽/映射/单双通道/bitmapping写成可核对项。

杭州立煌科技有限公司从2009年起一直专注LCD液晶屏行业,供应京东方(BOE)、天马(TIANMA)、龙腾(IVO)、友达(AUO)、群创(Innolux)、京瓷(Kyocera)等LCD工业液晶屏原厂原包原装现货,咨询:19157671329